- 4.3절의 데이터패스에 단순한 제어기능을 추가해 단순한 구현을 만들고자 함.

* 단순한 제어기능 : ALU 제어, 주 제어 유닛의 설계

* 단순한 구현 : add, sub, AND, OR, slt 등 명령어들

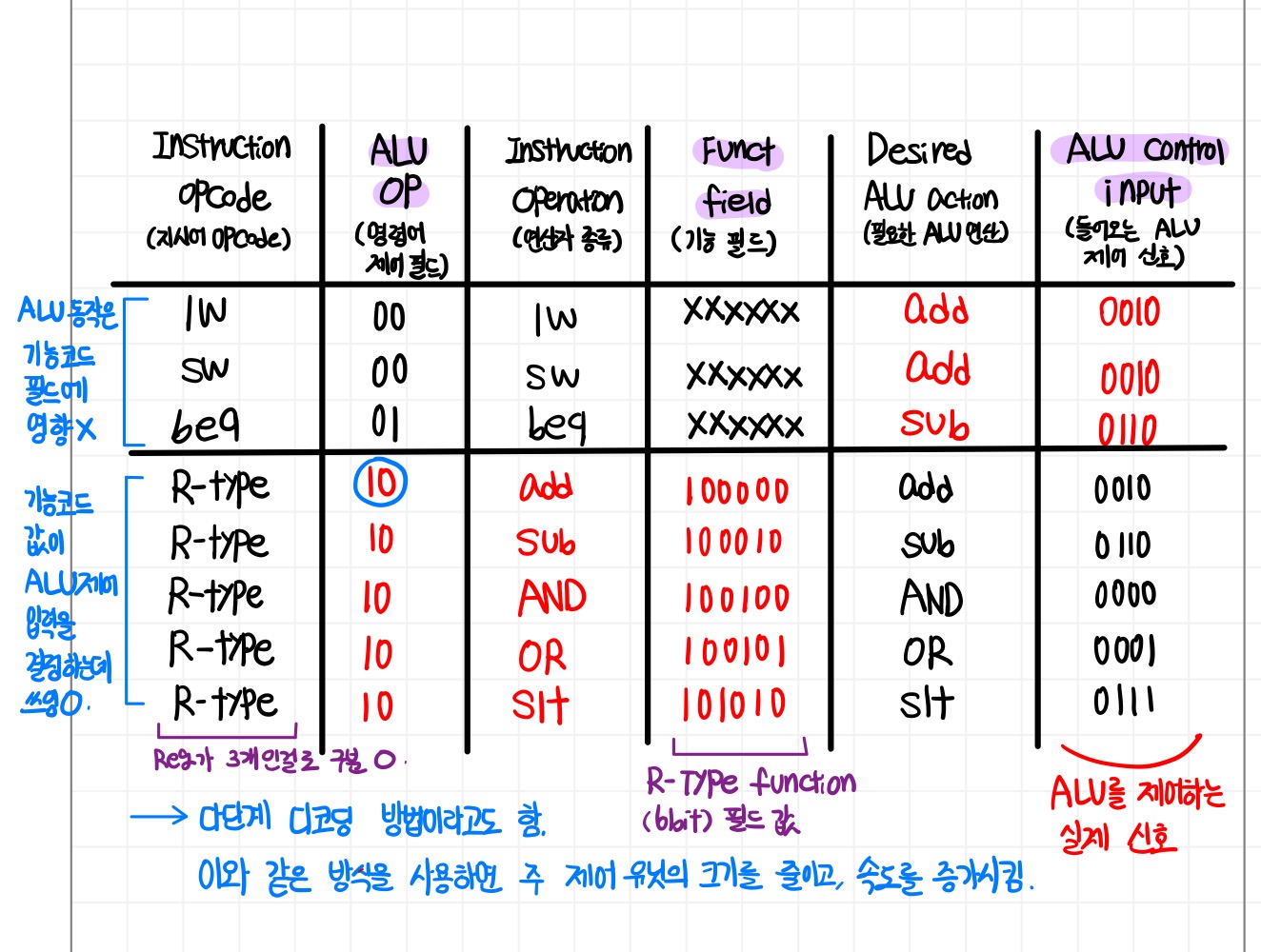

1. ALU 제어

1) ALU제어 신호의 종류 6가지

- MIPS는 제어입력 4개를 사용하는 다음 6개 조합을 정의하고 있다.

| ALU control lines | Function |

| 0000 0001 0010 0110 0111 1100 |

AND OR add sub slt NOR |

* ALU는 명령어 종류에 따라 5가지(초록색) 기능 중 하나를 수행하게 됨.

2) 명령어별 ALU 제어 신호

* ALUop제어(2bit) + 기능 코드(6bit) = ALU제어 입력(4bit)

| Instruction OPcode (지시어 opcode) |

ALU OP (명령어 제어 필드) |

Instruction Operation (연산자 종류) |

Funct field (기능 필드) |

Desired ALU action (필요한 ALU 연산) |

ALU control input (들어오는 ALU 제어신호) |

| lw sw beq |

00 00 01 |

lw sw beq |

xxxxxx xxxxxx xxxxxx |

add add sub |

0010 0010 0110 |

| R-type R-type R-type R-type R-type |

10 10 10 10 10 |

add sub AND OR slt |

100000 100010 100100 100101 101010 |

add sub AND OR slt |

0010 0110 0000 0001 0111 |

3) 4bit ALU제어신호를 위한 진리표

* 진리표 : 입력이 가질 수 있는 모든 값을 나열하고, 각 경우의 출력값을 보이는 논리 연산 표현방법

- 입력된 명령어에 따른, 두 가지 입력 필드에 따라(ALUop,Func field), 4bit ALU제어 값이 어떻게 실행되는지를 보여준다.

| ALUop(제어필드) | Fucnt Field | Operation (발생하는 ALU 제어신호) |

비고 |

| 00 x1 |

xxxxxx xxxxxx |

0010 0110 |

둘다 0이면 sw.lw op값 1인건, beq밖에 없음. |

| 1x 1x 1x 1x 1x |

xx0000 xx0010 xx0100 xx0101 xx1010 |

0010 0110 0000 0001 0111 |

add sub AND OR slt |

- 이 진리표가 만들어지면, 최적화후 게이트로 변환작업을 기계적으로 수행한다.

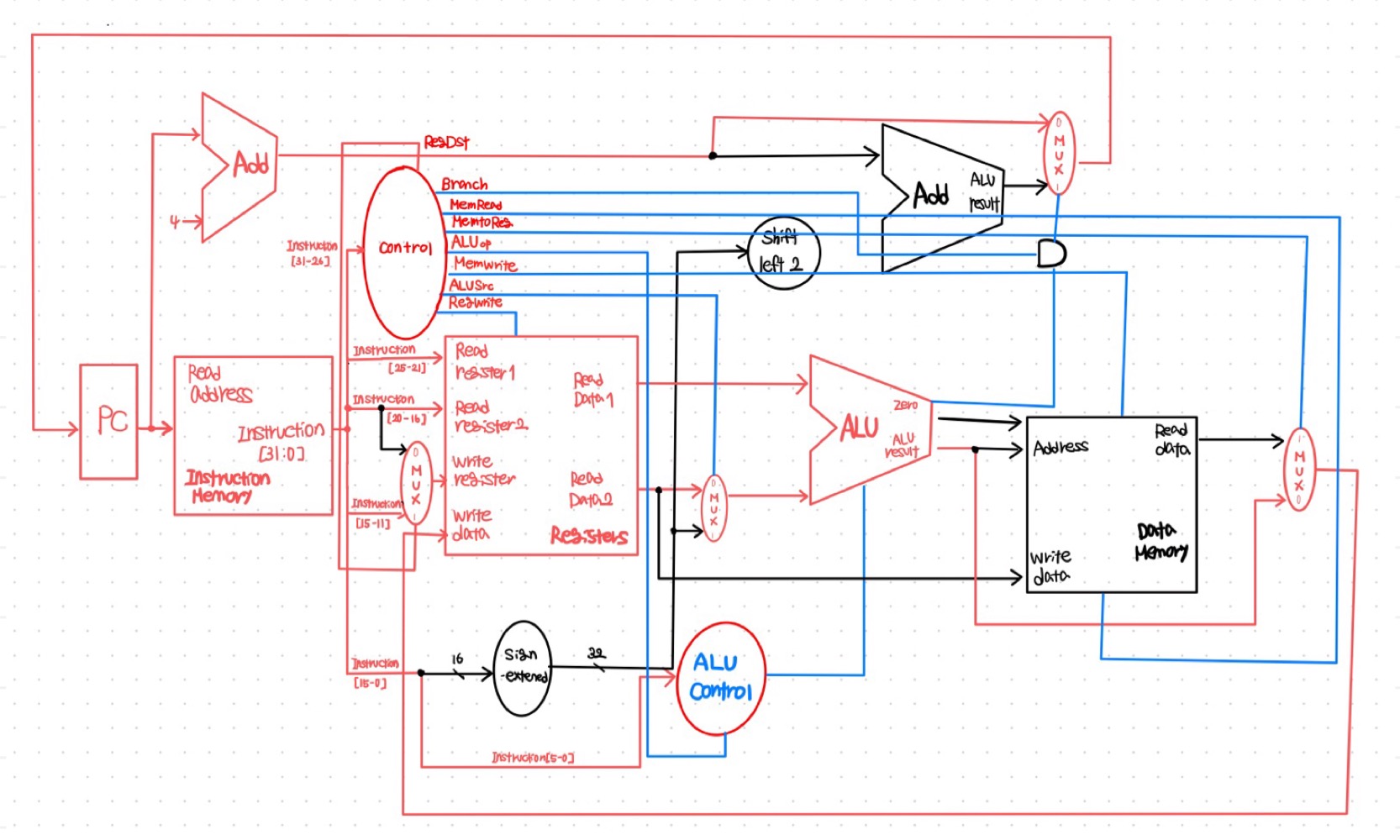

2. 주 제어 유닛의 설계

- 명령어 필드를 데이터패스에 연결하는 방법을 이해하기.

1) 제어신호와 멀티플랙서가 있는 데이터패스

2) 7개 제어신호의 기능(=제어선의 기능)

| 신호 이름 | 인가되지 않은 경우(0) | 인가된 경우(1) |

| RegDst | 명령어 rt필드(20:16)가 Write reg로 입력 |

명령어 rd필드(15:11)가 write reg로 입력 |

| Regwrite | 아무일도 발생하지 X | write register 입력이 지정하는 레지스터에 write Data 입력 값을 쓴다. |

| ALUSrc | 레지스터 파일의 두 번째 출력(Read Data2)가 ALU의 두 번째 피연산자가 된다. | 명령어의 하위 16bit가 부호확장되어 ALU의 두 번째 피연산자가 된다. |

| PCSrc | PC+4가 새로운 PC 값이 된다. | 분기 목적지 주소가 새로운 PC값이 된다. |

| MemRead | 아무일도 발생하지 X | Address 입력이 지정하는 데이터 메모리 내용을 Read Data 출력으로 내보보낸다. |

| MemWrite | 아무일도 발생하지 X | Address 입력이 지정하는 데이터의 메모리 내용을 Write Data 입력값으로 바꾼다. |

| MemtoReg | ALU출력이 레지스터의 write data 입력이 된다. | 데이터 메모리 출력이 레지스터의 Write Data 입력이 된다. |

3) 제어유닛 (Control Unit)

- 제어신호(Contorl)은 제어신호 중 하나를 제외한(PCSrc제외 : 제어유닛으로부터 직접 나오는 값이 아니고, 만들어야 하는 신호임), 나머지 모두를 명령어의 OPcode필드만 보고 결정할 수 있다.

1. 제어 유닛의 입력

: 명령어의 6bit OPcode 필드

2. 제어 유닛의 출력

: 멀티플랙서를 제어하는데 쓰이는 3개의 1bit신호 (RegDst, ALUSrc, MemtoReg)

: 레지스터 파일과 데이터 메모리에서 읽고 쓰는 것을 제어하기 위한 3개의 신호 (RegWrite, MemRead, MemWrite)

: 분기할지 말지를 판단하는데 쓰이는 1bit 신호(Branch)

: ALU를 위한 2bit 제어신호 (ALUop)

3. AND게이트

: 분기 제어신호와 ALU의 zero출력을 결합하는데 사용되는 AND게이트 출력은, PC 다음 값을 선택하는데 쓰인다.

3. 데이터패스의 동작 (명령어에 따른 데이터패스와 제어신호)

1) R형식 명령어의 실행과정

1. 명령어를 명령어 메모리에서 가져오고, PC값을 증가시킨다.

2. 두 레지스터(Read register 1,2)를 레지스터 파일로부터 읽는다. 이 단계에서 주 제어유닛이 제어선들의 값들을 계산한다.

3. ALU는 읽어들인 값들에 대해 연산을 하는데, 기능코드(명령어의 funct 필드인 비트 5:0)를 사용하여 ALU 제어신호를 만든다.

4. ALU 결과값이 레지스터 파일의 Write reg에 기록된다.

- 목적지 레지스터는 명령어의 비트 15:11을 이용해 선택한다.

- R형식 명령어의 제어신호

| RegDst | ALUSrc | MemtoReg | RegWrite | MemRead | Memwrite | Branch | ALUop |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 10 |

2) 적재(lw)명령어의 실행과정

1. 명령어를 명령어 메모리에서 가져오고 PC값을 증가킨다.

2. 레지스터(Read Register)의 값을 레지스터 파일로부터 읽어 값을 계산한다.

3. ALU는 레지스터 파일에서 읽어들인 Read Register의 주소값과, 명령어의 하위 16bit(OFFSET) 부호확장한 값과의, 합을 구한다.

4. ALU 계산결과(합)을 메모리 접근을 위한 주소로 사용해 메모리를 읽는다.

5. 메모리 유닛에서 가져온 데이터를 레지스터 파일의 Write Register[20:16]에 기록한다.

- 적재(lw) 명령어의 제어신호

| RegDst | ALUSrc | MemtoReg | RegWrite | MemRead | Memwrite | Branch | ALUop |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 00 |

3) 저장(sw)명령어의 실행과정

1. 명령어를 명령어 메모리에서 가져오고 PC값을 증가시킨다.

2. 레지스터(Read Register)의 값을 레지스터 파일로부터 읽어 값을 계산한다.

3. ALU는 레지스터 파일에서 읽어들인 Read Register의 주소값과, 명령어의 하위 16bit(OFFSET) 부호확장한 값과의, 합을 구한다.

4. ALU 계산 결과(합)을 메모리 접근을 위한 주소로 사용해, 데이터 메모리에 쓰기.

- 저장(sw) 명령어의 제어신호

| RegDst | ALUSrc | MemtoReg | RegWrite | MemRead | Memwrite | Branch | ALUop |

| X | 1 | X | 0 | 0 | 1 | 0 | 00 |

4) 분기(beq)명령어의 실행과정

1. 명령어를 명령어 메모리에서 가져오고 PC값을 증가시킨다.

2. 두 레지스터(Read Register 1,2)의 값을 레지스터 파일로부터 읽고, 해당 값을 계산한다.

3. ALU는 레지스터 파일에서 읽어들인 값들에 대해 뺄셈을 한다. 그리고 명령어의 하위 16bit(OFFSET)를 부호확장한후 2bit자리이동한 값에다, PC+4를 더한다. 결과 값이 분기 목적지 주소이다.

4. 어떤 덧셈기의 값을 PC에 저장할지, ALU의 zero 출력을 이용하여 판단한다.

- 분기(beq) 명령어의 제어신호

| RegDst | ALUSrc | MemtoReg | RegWrite | MemRead | Memwrite | Branch | ALUop |

| X | 0 | X | 0 | 0 | 0 | 1 | 01 |

5) 점프(jump)명령어의 실행과정

- jump는 직접, 워드 주소를 사용한다.

- 즉, 새로운 멀티플랙서와 제어신호가 필요하다.

- 점프(jump) 명령어의 제어신호

| RegDst | ALUSrc | MemtoReg | RegWrite | MemRead | Memwrite | Branch | ALUop | jump |

| X | X | X | 0 | 0 | 0 | X | XX | 1 |

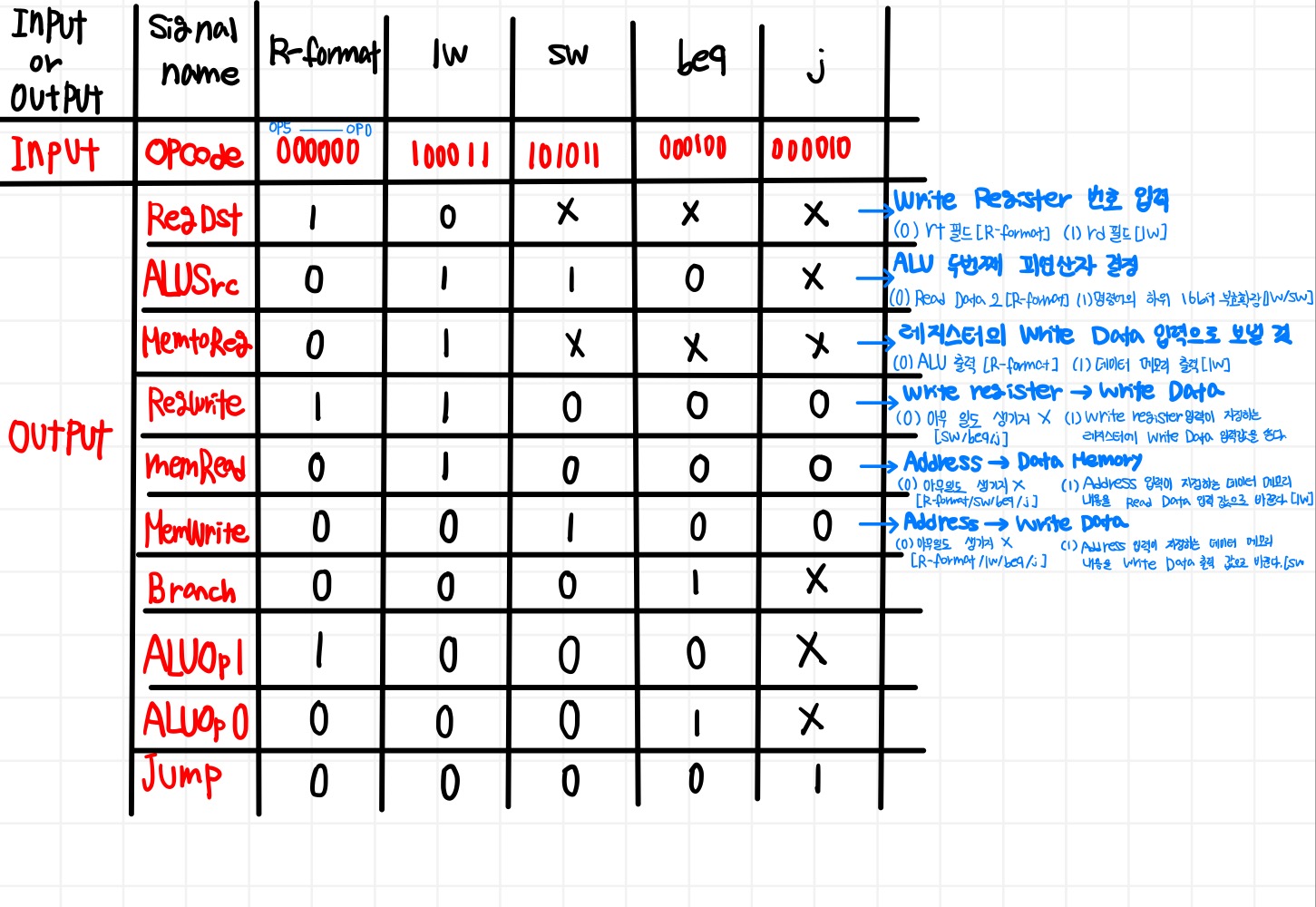

4. 제어 유닛의 완성

1) 각 명령어의 제어 신호 종합

- opcode의 이진수 인코딩을 이용해 각 출력의 진리표를 만듦.

5. 단일 사이클 구현은 오늘날 왜 사용되지 않는가?

- 단일 사이클 설계가 올바르게 작동된다 하더라도, 비효율성 때문에 현대에서 잘 사용되지 않는다.

* 클럭 사이클이 모든 명령어에 대해 같은 길이를 가져야 함.

* 클럭 사이클은 가장 긴 경로로 결정 (lw-5개 유닛을 차례로 사용)

* CPI 값은 1이지만, 단일 사이클구현은 클럭사이클이 너무 길기 때문에 전체 성능이 좋지 않음.

- 이후, 파이프라이닝을 통해, 처리율(효율성)이 높은 기술을 구현하게 된다.

| * 유의사항 - 아직 공부하고 있는 문과생 코린이가, 정리해서 남겨놓은 정리 및 필기노트입니다. - 정확하지 않거나, 틀린 점이 있을 수 있으니, 유의해서 봐주시면 감사하겠습니다. - 혹시 잘못된 점을 발견하셨다면, 댓글로 친절하게 남겨주시면 감사하겠습니다 :) |

'문과 코린이의, [컴퓨터 구조] 기록 > 컴퓨터구조 4강' 카테고리의 다른 글

| [문과 코린이의 IT기록장] 컴퓨터 구조 - 4.6. 파이프라인 데이터패스 및 제어 (1) | 2021.01.20 |

|---|---|

| [문과 코린이의 IT기록장] 컴퓨터 구조 - 4.5. 파이프라이닝에 대한 개관 (6) | 2021.01.19 |

| [문과 코린이의 IT기록장] 컴퓨터 구조 - 4.3. 데이터패스 만들기 (2) | 2021.01.17 |

| [문과 코린이의 IT 기록장] 컴퓨터 구조 - 4.2.논리 설계 관례 (0) | 2021.01.17 |

| [문과 코린이의 IT기록장] 컴퓨터 구조 - 4.1. 프로세서(CPU) (0) | 2021.01.17 |